| ■ | 豊富な最先端技術の開発経験に基づく超高速・広帯域メモリ設計技術を用いた4、8、12、16積層/パッケージ製品開発 |

| ① JEDEC標準DRAM | :LP3、LP4、LP5、DDR4、DDR5、HBM |

| ② カスタムメモリ | :ワイドI/O(×64以上)、多チャネル(4、8)/パッケージ |

| ③ 積層メモリ | :Wafer on Wafer |

| ④ 2.5、3D実装 | |

| ⑤ 超高速、低消費電力パッケージ | |

| ■ | 豊富な最先端技術の開発経験に基づく超高速・広帯域メモリ設計技術を用いた4、8、12、16積層/パッケージ製品開発 |

| ① JEDEC標準DRAM | :LP3、LP4、LP5、DDR4、DDR5、HBM |

| ② カスタムメモリ | :ワイドI/O(×64以上)、多チャネル(4、8)/パッケージ |

| ③ 積層メモリ | :Wafer on Wafer |

| ④ 2.5、3D実装 | |

| ⑤ 超高速、低消費電力パッケージ | |

| ■ | 独自開発事例 |

| プロジェクト | 技術 | 特徴 | 開発状況 |

|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ■ | 設計受託 |

カスタムインタフェースを含む各種メモリ(DRAM/SRAM/MRAM)の開発において20件以上の設計実績があります。

| ■ | 特許実績(登録済み件数) |

2022年12月現在 日本:22 米国:13 中国:8 合計:43件

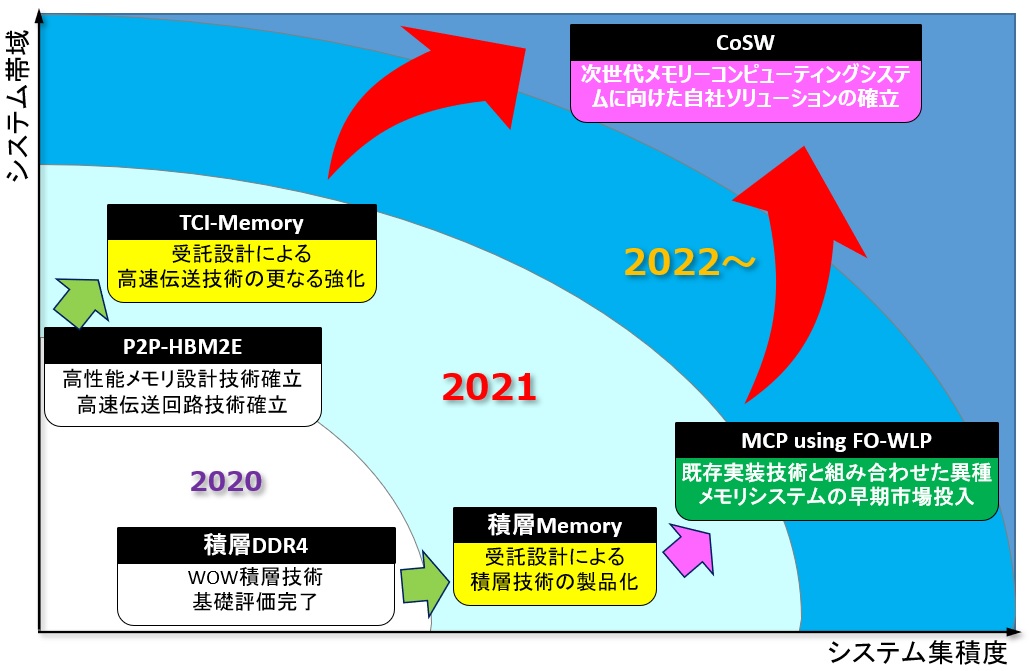

| P2P | :Pad to Pad interconnect | TCI | :ThruChip Interface |

| FO-WLP | :Fan Out Wafer Level Package | MCP | :Multi Chip Package |

| CoSW | :Chip on Stacked Wafer | WOW | :Wafer on Wafer |

Copyright © 2026 UltraMemory Inc. All Rights Reserved.